|

處理器(CPU)結(jié)構(gòu)

處理器一般指中央處理器,中央處理器(CPU, Central Processing Unit)是一塊超大規(guī)模的集成電路,是一臺計算機(jī)的核心(Core)和控制核心(Control Unit)。它的功能主要是解釋計算機(jī)指令以及處理計算機(jī)軟件中的數(shù)據(jù)。大多數(shù)現(xiàn)代電路設(shè)計都是用信號線上的高電壓和低電壓來表示不同的位值。要實現(xiàn)一個數(shù)字系統(tǒng)需要三個主要的組成部分:

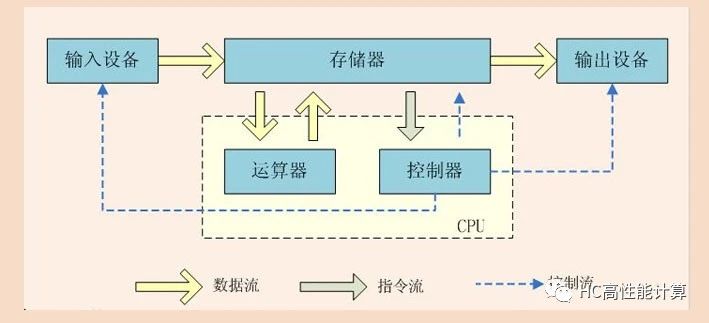

根據(jù)馮·諾依曼思想,計算機(jī)采用二進(jìn)制作為數(shù)制基礎(chǔ),必須包含: 運(yùn)算器、控制器、存儲設(shè)備,以及輸入輸出設(shè)備,如下圖所示:

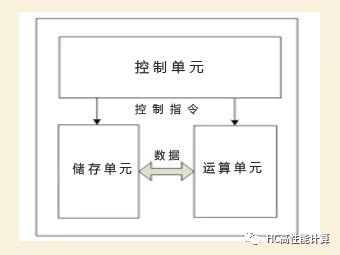

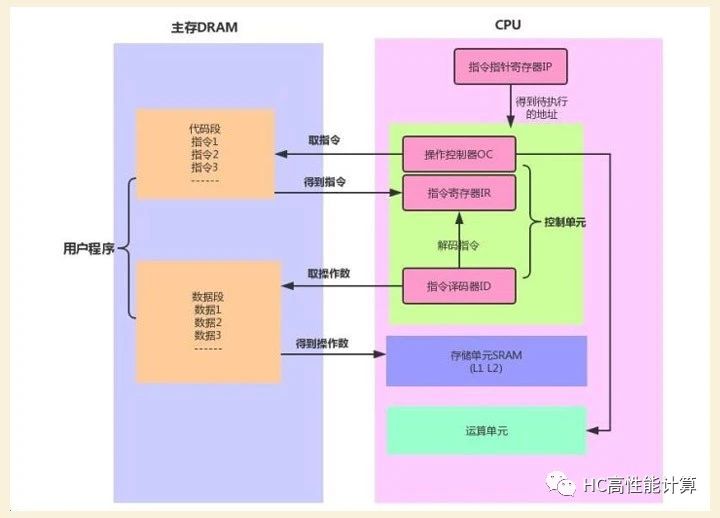

CPU的根本任務(wù)就是執(zhí)行指令,對計算機(jī)來說最終都是一串由“0”和“1”組成的序列。CPU從邏輯上可以劃分成3個模塊,分別是控制單元、運(yùn)算單元和存儲單元,這三部分由CPU內(nèi)部總線連接起來。如下所示:

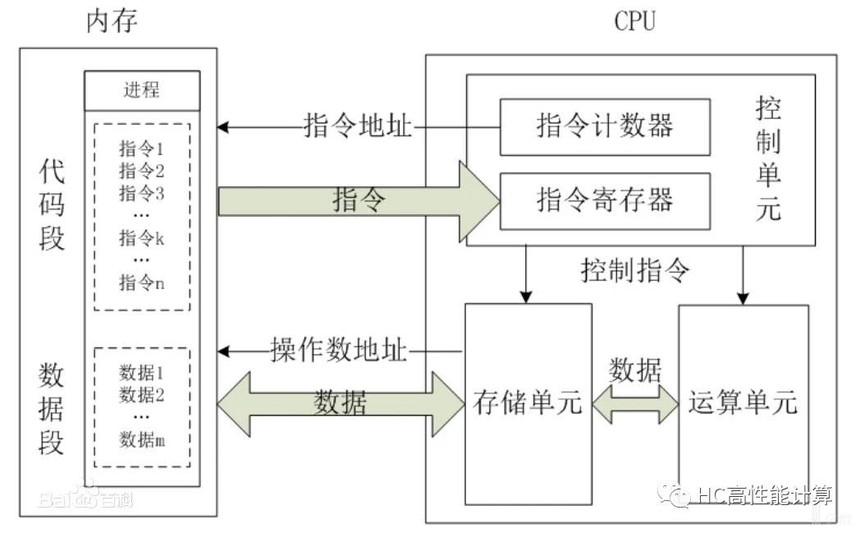

控制單元 控制單元是整個CPU的指揮控制中心,由指令寄存器IR(Instruction Register)、指令譯碼器ID(Instruction Decoder)和操作控制器OC(Operation Controller)等,對協(xié)調(diào)整個電腦有序工作極為重要。它根據(jù)用戶預(yù)先編好的程序,依次從存儲器中取出各條指令,放在指令寄存器IR中,通過指令譯碼(分析)確定應(yīng)該進(jìn)行什么操作,然后通過操作控制器OC,按確定的時序,向相應(yīng)的部件發(fā)出微操作控制信號。操作控制器OC中主要包括節(jié)拍脈沖發(fā)生器、控制矩陣、時鐘脈沖發(fā)生器、復(fù)位電路和啟停電路等控制邏輯。 運(yùn)算單元 運(yùn)算單元是運(yùn)算器的核心。可以執(zhí)行算術(shù)運(yùn)算(包括加減乘數(shù)等基本運(yùn)算及其附加運(yùn)算)和邏輯運(yùn)算(包括移位、邏輯測試或兩個值比較)。相對控制單元而言,運(yùn)算器接受控制單元的命令而進(jìn)行動作,即運(yùn)算單元所進(jìn)行的全部操作都是由控制單元發(fā)出的控制信號來指揮的,所以它是執(zhí)行部件。 存儲單元 存儲單元包括CPU片內(nèi)緩存和寄存器組,是CPU暫時存放數(shù)據(jù)的地方,里面保存著那些等待處理的數(shù)據(jù),或者已經(jīng)處理過的數(shù)據(jù),CPU訪問寄存器所用的時間比直接訪問內(nèi)存的時間短。采用寄存器,可以減少CPU訪問內(nèi)存的次數(shù),從而提高了CPU的工作速度。但因為受到芯片面積和集成度限制,寄存器組的容量不可能很大。寄存器組可分為專用寄存器和通用寄存器。專用寄存器的作用是固定的,分別寄存相應(yīng)的數(shù)據(jù)。而通用寄存器作用廣泛并可由程序員規(guī)定其用途,通用寄存器的數(shù)目因微處理器而不同。 工作原理 CPU的工作原理概括如下圖:

總的來說,CPU從內(nèi)存中一條一條地取出指令和相應(yīng)的數(shù)據(jù),按照指令操作碼的規(guī)定,對數(shù)據(jù)進(jìn)行運(yùn)算處理,直到程序執(zhí)行完畢為止。 更細(xì)一點(diǎn)的說,控制單元是CPU的控制中心,CPU需要通過它才知道下一步做什么,也就是執(zhí)行什么指令,控制單元包含指令寄存器(IR)、指令譯碼器(ID)和操作控制器(OC)。當(dāng)程序被加載進(jìn)內(nèi)存后,指令就在內(nèi)存中了,這個時候說的內(nèi)存是獨(dú)立于CPU外的主存設(shè)備,也就是PC機(jī)中的內(nèi)存條。指令指針寄存器IP指向內(nèi)存下一條待執(zhí)行指令的地址,控制單元根據(jù)IP寄存器的指向,將主存中的指令加載到指令寄存器,這個指令寄存器也是一個存儲設(shè)備,不過集成在CPU內(nèi)部。指令從主存到達(dá)CPU后只是一串串010101的二進(jìn)制串,還需要通過譯碼器解碼,分析出操作碼是什么,操作數(shù)在哪,之后就是具體的運(yùn)算單元進(jìn)行算數(shù)運(yùn)算(加減乘除),邏輯運(yùn)算(比較,位移)。 CPU指令執(zhí)行過程大致為:取址(從主存獲取指令放到寄存器)→ 譯碼(從主存獲取操作數(shù)放到高速緩存L1)→ 執(zhí)行(運(yùn)算)

上圖中 CPU 內(nèi)部集成的存儲單元 SRAM ,正好和主存中的 DRAM 對應(yīng), RAM 是隨機(jī)訪問內(nèi)存,就是給一個地址就能訪問到數(shù)據(jù),而磁盤這種存儲媒介必須順序訪問,而 RAM 又分為動態(tài)和靜態(tài)兩種,靜態(tài) RAM 由于集成度較低,一般容量小,速度快,而動態(tài) RAM 集成度較高,主要通過給電容充電和放電實現(xiàn),速度沒有靜態(tài) RAM 快,所以一般將動態(tài) RAM 做為主存,而靜態(tài) RAM 作為 CPU 和主存之間的高速緩存 (cache),用來屏蔽 CPU 和主存速度上的差異,也就是我們經(jīng)常看到的 L1 , L2 緩存。每一級別緩存速度變低,容量變大。 處理器的單元邏輯 更細(xì)一點(diǎn),從實現(xiàn)的功能方面看,CPU大致可分為如下八個邏輯單元: (1)指令寄存器 :它是芯片上的指令倉庫,有了它CPU就不必停下來查找計算機(jī)內(nèi)存中的指令,從而大幅提高了CPU的運(yùn)算速度。 (2)指令譯碼器 :它負(fù)責(zé)將復(fù)雜的機(jī)器語言指令解譯成運(yùn)算邏輯單元(ALU)和寄存器能夠理解的簡單格式,就像一位外交官。 (3)控制單元 :既然指令可以存入CPU,而且有相應(yīng)指令來完成運(yùn)算前的準(zhǔn)備工作,背后自然有一個扮演推動作用的角色——它便是負(fù)責(zé)整個處理過程的操作控制器。根據(jù)來自譯碼單元的指令,它會生成控制信號,告訴運(yùn)算邏輯單元(ALU)和寄存器如何運(yùn)算、對什么進(jìn)行運(yùn)算以及對結(jié)果進(jìn)行怎樣的處理。 (4)寄存器 :它對于CPU來說非常的重要,除了存放程序的部分指令,它還負(fù)責(zé)存儲指針跳轉(zhuǎn)信息以及循環(huán)操作命令,是運(yùn)算邏輯單元(ALU)為完成控制單元請求的任務(wù)所使用的數(shù)據(jù)的小型存儲區(qū)域,其數(shù)據(jù)來源可以是高速緩存、內(nèi)存、控制單元中的任何一個。 (5)邏輯運(yùn)算單元(ALU) :它是CPU芯片的智能部件,能夠執(zhí)行加、減、乘、除等各種命令。此外,它還知道如何讀取邏輯命令,如或、與、非。來自控制單元的訊息將告訴運(yùn)算邏輯單元應(yīng)該做些什么,然后運(yùn)算單元會從寄存器中間斷或連續(xù)提取數(shù)據(jù),完成最終的任務(wù)。 (6)預(yù)取單元 :PU效能發(fā)揮對其依賴非常明顯,預(yù)取命中率的高低直接關(guān)系到CPU核心利用率的高低,進(jìn)而帶來指令執(zhí)行速度上的不同。根據(jù)命令或要執(zhí)行任務(wù)所提出的要求,何時時候,預(yù)取單元都有可能從指令高速緩存或計算機(jī)內(nèi)存中獲取數(shù)據(jù)和指令。當(dāng)指令到達(dá)時,預(yù)取單元最重要的任務(wù)就是確保所有指令均排列正確,然后發(fā)送給譯碼單元。 (7)總線單元 :它就像一條高速公路,快速完成各個單元間的數(shù)據(jù)交換,也是數(shù)據(jù)從內(nèi)存流進(jìn)和流出CPU的地方。 (8)數(shù)據(jù)高速緩存 :存儲來自譯碼單元專門標(biāo)記的數(shù)據(jù),以備邏輯運(yùn)算單元使用,同時還準(zhǔn)備了分配到計算機(jī)不同部分的最終結(jié)果。 通過以上介紹可以看出CPU雖小,方寸之地卻能容納大世界,內(nèi)部更像一個發(fā)達(dá)的裝配工廠,環(huán)環(huán)相扣,層層相套。正因為有了相互間的協(xié)作配合,才使得指令最終得以執(zhí)行,才構(gòu)成了圖文并茂、影像結(jié)合的神奇數(shù)字世界 。 上一篇集群常用操作命令下一篇定制化產(chǎn)品咨詢 |